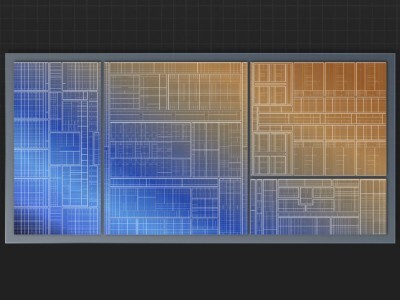

Az Intel az Innovation 2023 rendezvényén kapásból a Meteor Lake leleplezésével kezdett, amely a vállalat új, mobil gépeket megcélzó platformja lesz. A fejlesztés négy chipletből épül fel, amelyek egy 22 nm-es Intel node-on készülő Base tile-on helyezkednek el. Utóbbi biztosítja a a chipletek összeköttetését a Foveros technológián keresztül.

Az egyes chipletek szempontjából az Intel egyedül az úgynevezett Compute tile nevű CPU chipletet gyártja majd, méghozzá az Intel 4 nevű 7 nm-es osztályú eljárásán. A többi három chiplet a TSMC-nél fog készülni. Ezek közül a grafikus vezérlőt tartalmazó Graphics tile lapka 5 nm-es, míg a SoC tile és az IO tile chiplet 6 nm-es node-on érkezik.

A fizikai felépítés már önmagában elég komplex, és a gyártást a Foveros technológia is igen drágává teszi, de az Intel még az egyes chipletek tekintetében is szolgál meglepetésekkel. Logikus lenne azt gondolni, hogy a processzorrész teljes egészében a Compute tile-ban helyezkedik el, de a Santa Clara-i óriáscég alaposan csavart a korábban bevetett hibrid dizájnon, amit újonnan 3D hibridként emlegetnek, de valójában szó sincs harmadik dimenzióról. A lényeg csupán annyi, hogy a Meteor Lake-ben 16 darab nem egységes teljesítményű mag dolgozhat. Ezek közül 6 darab nagy teljesítményű, Redwood Cove kódnevű P-mag, 8 darab kisebb teljesítményű, Crestmont kódnevű E-mag, illetve 2 darab úgynevezett alacsony fogyasztású (szintén Crestmont) E-mag lehet. Mostantól tehát nem kettő, hanem három eltérő magteljesítménnyel kell számolni, és mivel a kisebb magok nem támogatták a Hyper-Threadinget, így a futtatható szálak száma 22 lesz. A P-magok, illetve a normál E-magok a Compute tile-ban helyezkednek el, viszont az alacsony fogyasztású két E-mag már a SoC tile része, vagyis eléggé el vannak választva a fő processzorrésztől. Emiatt az ütemezésért felelős Thread Director is megváltozik.

Az Intel stratégiája itt annyi, hogy a befutó feladatot a Thread Director megvizsgálja, és ha reálisan futtatható a SoC tile E-magjain, akkor megpróbálja ott tartani. Ha a teljesítménylimitek miatt ez nem lehetséges, akkor Compute tile-ra másolja a rendszer az adatokat, és a normál E-magok kerülnek előtérbe, hátha azok elég gyorsak. Ha ez sem jó, akkor utolsó mentsvárként maradnak a legnagyobb teljesítményű P-magok. Az Intel szerint az alulról építkezés azért jobb módszer, mert a korábbi hibrid dizájnoknál a feladatok nagy része a P-magokon kezdett, de időnként értelmetlenül, mert az E-mag is elég lett volna. Ezzel a rendszer veszített az energiahatékonyságából, a Meteor Lake viszont lépcsőzetesen építkezik, és csak akkor nyúl a P-magokhoz, ha az elengedhetetlenül szükséges. Ilyen formában a hatékonyság maximalizálása a cél.

A másik fontos eleme a dizájnnak a Graphics tile, amely Xe-LPG architektúrára épül. Utóbbi a dedikált GPU-knál alkalmazott Xe-HPG technikai képességeit másolja, beleértve a sugárkövetés gyorsítását is, csak az Intel kihagyta a rendszerből az XMX nevű mátrixfeldolgozókat. Ennek amúgy sincs nagy haszna, hiszen csak az XeSS eljárás működésének javítására szolgál, de utóbbi képes szabványos kódutat használva a vektormotorokon is futni, utóbbiakból pedig egy multiprocesszor 16 darabot tartalmaz. Ez a teljes IGP-re levetítve 128 darab 256 bites vektormotort jelent.

A további részegységek a SoC tile-ban találhatók, ide került az AV1-es formátum dekódolását biztosító multimédiás blokk, illetve a HDMI 2.1-et és DisplayPort 2.1-et kezelő kijelzőmotor, a kétcsatornás memória-, illetve a PCI Express vezérlő, továbbá egy új részegység is bemutatkozik, amit az Intel NPU (Neural Processing Unit) néven emleget. Ez az AI feladatok gyorsítására lett kialakítva, és az alapja a Movidius dizájnból ered. Végül az IO tile a szükséges interfészek fizikai implementációját tartalmazza. Újítás még az ISSE (Intel Silicon Security Engine), amely a platformszintű biztonságon javíthat.

Az Intel szerint mindegyik chipletből több verzió készül, annak függvényében, hogy mennyi aktív részegységgel dolgozik az adott processzor. Ennek a költségcsökkentésben lesz szerepe, ugyanis maga a Foveros sajnos nem éppen olcsón alkalmazható technológia, vagyis az adott CPU-hoz eleve nem használt feldolgozók esetében az az optimális, ha a lehető legtöbb részegységet eleve lehagyják a lapkákról.

A Meteor Lake kódnevű processzorok december közepén érkezhetnek, de első körben valószínűleg csak pár modellről lesz szó.