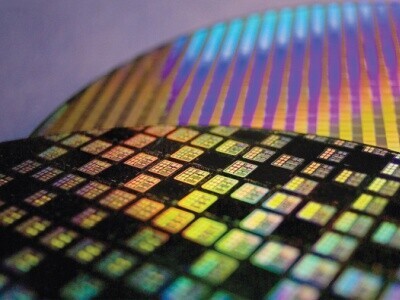

A TSMC felvázolta, hogy milyen fejlesztések várhatók a jövőben, így konkrét útitervet kaptunk arról, hogy 3 és 2 nm-es eljárásokon milyen node-okat vet be a bérgyártó.

A tajvani bérgyártó 3 nm-en konkrétan négy node-ot is tervez. Elsőként az N3 érkezik, amelyen a tömeggyártás még idén megkezdődhet. Ez az eljárás az 5 nm-es node-hoz viszonyítva akár 30%-kal jobb fogyasztási adatokat és 15%-kal jobb teljesítményt kínál majd, de a kezdeti szakaszban számolni kell az alacsonyabb kihozatali aránnyal is. Emiatt sokan inkább az N3E node felé nézelődhetnek, amely már egy második generációs fejlesztés, és 10-20% közötti további javulás mellé elég sok flexibilitást kínál majd a megrendelők számára, noha a tömeggyártása csak a következő esztendő második felében indul.

A TSMC az alapvető 3 nm-es node-ok mellé amolyan specializált alternatívákat is kínál: az N3P a teljesítménycentrikus, az N3S a tranzisztorsűrűségre optimalizált, míg az N3X a HPC-piacra tervezett variáns lesz.

A 3 nm-es eljárás kapcsán fontos kiemelni, hogy a FinFET tranzisztorstruktúra már nem optimális, mivel nehezen skálázható ilyen csíkszélességen, de a tajvani bérgyártó előállt a FinFlex technológiával, ami ezen javíthat valamennyit. A FinFlex lényege az, hogy egy chiptervező egy adott blokkon belül nem lesz arra kényszerítve, hogy a teljes blokkot egységes könyvtári elemekből építse fel. Egyszerűen válogatni lehet a lehetőségek között az egyes áramkörök igényei alapján, ami elég sok szabadságot kínál a tervezés szempontjából, noha a munkafolyamat komplexitását kétségtelenül növeli.

A csúcstechnológiát tekintve egy ideje már ismert, hogy a TSMC 2 nm-en vált GAAFET tranzisztorstruktúrára. Erről már volt szó a Samsung kapcsán, hiszen a dél-koreai óriáscég azt a váltást 3 nm-en lépi meg. A lényeg továbbra is a source és drain közötti, kikapcsolt állapotban jelentkező elektronszivárgás csökkentése. Anno, a jelenlegi modern eljárásoknál széleskörűen alkalmazott FinFET is emiatt lett bevezetve: a mérnökök ugyanis rájöttek arra, hogy ha a source és a drain kiemelkedik az alaprétegből a szigetelő fölé, akkor körbe tudják fogni a kapuelektródával. Ez a módszer azonban nem működik elég jól alacsonyabb csíkszélességen, és itt jön képbe a GAAFET, mivel ennél a megoldásnál a source és a drain közé nanohuzalok kerülnek, amiket teljesen közrefog a kapuelektróda, leszigetelve azokat.

A konkrét GAAFET implementációk tekintetében az a kérdés, hogy ezek a nanohuzalok milyenek legyenek, és mennyi legyen belőlük. Utóbbi szempontból jelenleg minden érintett úgy gondolja, hogy első körben három nanohuzal elég, de a számuk esetlegesen később növekedhet. A kialakítás tekintetében szintén több alternatíva létezik, mivel lehet alkalmazni konkrétan nanohuzalokat, vagy nanolapokat, esetleg nanoszalagokat. Technikailag ezek mind tekinthetők nanohuzalnak, a különbséget az adja, hogy miképpen vannak kialakítva. Például a nanolapok és a nanoszalagok esetében szélességük némileg módosítható, ami bizonyos mértékű flexibilitást ad a dizájnok kialakításánál. A Samsung nanolapokat alkalmaz a 3 nm-es eljárásán, míg az Intel a saját, Intel 20A-nak nevezett 5 nm-es osztályú implementációjánál a nanoszalagokat választotta. A TSMC a 2 nm-es node-ján a Samsunghoz hasonlóan nanolapokat használ majd, ezzel biztosítva némi rugalmasságot a partnereknek a GAAFET-re tervezett lapkák tekintetében.

A TSMC szerint a 2 nm-es eljárás az N3E node-hoz viszonyítva akár 30%-kal jobb fogyasztási adatokat és 15%-kal jobb teljesítményt kínálhat, a kísérleti gyártás megkezdése pedig 2025-ben esedékes.