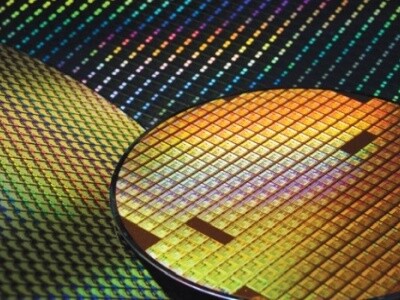

A DigiTimes információi szerint az elmúlt pár évben megállíthatatlanul száguldó TSMC a 3 nm-es node kapcsán némi problémába ütközött. Ez az a gyártási eljárás, amivel a tajvani bérgyártó igen nagyot kockáztat, mivel a Samsunggal ellentétben nem térnek át a GAAFET tranzisztorstruktúrára, hanem maradnak a FinFET-nél, amiről tudni lehetett, hogy nem kifejezetten jó a skálázódása ilyen kis csíkszélességre.

Persze a TSMC úgy gondolta, hogy a potenciálisan felmerülő gondokat még meg tudják oldani, és tulajdonképpen ez még ma is elképzelhető, de a friss pletykák alapján kihozatali nehézségei vannak a szóban forgó gyártási eljárásnak. Ez egyelőre a tajvani cég kommunikációjában nem látszik, továbbra is jónak tartják a fejlesztés eredményeit, de a DigiTimes forrása úgy tudja, hogy a TSMC folyamatosan felülvizsgálta a tervezett gyártástechnológiára szánt kínálatát, amit állítólag azért tesznek, hogy megtalálják a kihozatal szempontjából még optimális szintet.

A fentiekre utalhat az, hogy az eredeti N3 node-ot egy évvel később követi majd egy N3E verzió, ami a gyártási költségeket csökkenti, illetve állítólag készül egy N3B variáns is az egyes partnerek számára. Feltételezhető, hogy az eredeti 3 nm-es node kihozatala sokak számára nem elfogadható, így a TSMC próbálja az eljárást specializálni, hogy az ügyfeleik igényeit jobban le tudják fedni.

Azt nem tudni pontosan, hogy mely cégek érintettek a fentiektől. Egyelőre egyik vállalatnak sem jelent meg direkten az útitervében a TSMC 3 nm-es eljárása, noha feltételezhető, hogy már több cég is érdeklődött a gyártástechnológia iránt, csak ezt még nem kötötték a publikum orrára.