A Hynix még a nyáron prezentálta 4D NAND jövőképét, az első termék pedig meg is érkezett. Az új, 512 gigabites konstrukció 96 cellaréteget használ, a cellák pedig három bitet tárolnak, azaz TLC-s megoldásnak tekinthető a memória.

A 4D elnevezés természetesen ne tévesszen meg senkit, a lapka valójában háromdimenziós struktúrájú azzal a kis trükkel, hogy a CMOS logika nem a cellák mellé, hanem alá van elhelyezve. Ez a PUC, azaz a Periphery Under Cell technológia, ami igazából még egyedinek sem számít, mivel a Micron és az Intel igen hasonló dizájnt használ a 3D NAND érában, csak az említett vállalatok erre CuA (CMOS under Array) néven utalnak, de egyébként a Samsung is ilyen irányba fejleszt.

Kétségtelen viszont, hogy a PUC hasznos, mivel 30%-kal képes csökkenteni a lapka kiterjedését, ami a Hynix szerint a 49%-kal több kinyerhető chipet eredményez egy waferből a korábbi generációs, 72 cellarétegű, 512 gigabites 3D NAND fejlesztéshez viszonyítva. További extra, hogy a 30 és 25 százalékkal nő az írás és az olvasás melletti teljesítmény, illetve az I/O tempó elérheti az 1200 Mbps-ot, méghozzá 1,2 voltos feszültség mellett.

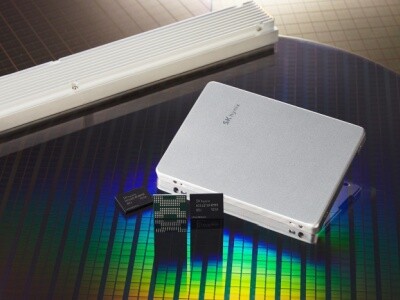

A technológia birtokában a Hynix itt nem áll meg, már készül az 1 terabites verzió, amelyből lesz TLC-s és QLC-s modell is. Mindemellett a vállalat új, 1 TB-os kapacitásig skálázódó SSD-szériát tervez a fenti lapka bevetésével, illetve saját vezérlővel és firmware-rel, a következő év során pedig jönnek majd a nagyvállalati környezetbe szánt SSD-k is.