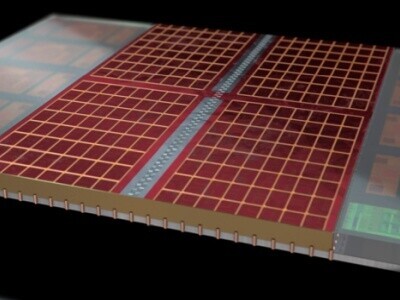

Az AMD még az idei Computexen mutatta be a 3D V-Cache-nek nevezett gyorsítótárát, amely lényegében egy extra 64 MB-os kapacitás a már meglévő Zen 3 chiplet fölé építve. A vállalat az idei Hot Chips alkalmával egy picit részletesebben is beszélt a technológiáról, amelyhez eleve úgy tervezték az eredeti chipletet, hogy később a 3D-s tokozás bevethető legyen.

Az AMD szerint a 3D V-Cache lesz a piacon az első, nagy teljesítményű 3D-s tokozási eljárás, ami valószínűleg igaz is lehet, ha a tényleges dizájnok idén, vagy a következő év első felében megjelennek. Ehhez hasonló az Intel-féle Foveros, de nagy különbség, hogy az alacsony teljesítményszintre van tervezve, nem véletlen, hogy eddig az igencsak visszafogott fogyasztású, Lakefield kódnevű fejlesztés használta.

Az alapkoncepció ugyan nagyon hasonló, de az AMD-féle 3D-s tokozás több szempontból is különbözik az Intel-féle Foverostól. Ezt nagyrészt az adja, hogy az AMD szerint erre a problémára nincs univerzális megoldás, az eltérő piacokra szánt dizájnokhoz, eltérő megoldások kellenek a 3D-s tokozás tekintetében. Ez egy nagyon lényeges tényezőből ered, az egyes dizájnok fogyasztása jelentősen eltérhet, ami hatványozottan nagy probléma a lapkák egymásra tokozásánál, hiszen a hőátadásnak optimálisnak kell lennie.

Az AMD a fenti gonddal úgy küzd meg, hogy a Foverosszal ellentétben nem F2F (Face-to-Face), hanem TSV (Through Silicon Via) érintkezőket használ. Utóbbi kivitelezése bonyolultabb, illetve drágább is, de nem csak két lapka tokozható egymásra, hanem több is, és ezeknek jóval nagyobb energia biztosítható, miközben a hőelvezetés a fémrétegeken, illetve az fémösszeköttetéseken át optimális lehet.

Amellett tehát, hogy az AMD 3D-s tokozása pusztán elméleti szinten ugyanúgy egymásra tokozható lapkákat kínál, egyáltalán nem ugyanazokat a piacokat célozza, mint például a Foveros. Éppen ezért, amíg az Intelnek nagy teljesítményű dizájnja nincs 3D-s tokozással, addig az AMD-nek kis teljesítmény dizájnja nem lesz ilyen formában.

A fentiek miatt a tokozási eljárások pusztán szakmai szempontból ugyan összehasonlíthatók, de az eltérő célpiac miatt más igényekre vannak tervezve, így nem meglepő, hogy az AMD 3D-s tokozási technológiája a TSV érintkezőkkel sokkal energiahatékonyabb, mint egy micro bump érintkezőkre alapozó megoldás. Az úgynevezett léptetés, vagyis két szomszédos láb középvonalai között mérhető távolság is sokkal kisebb, mindössze 9 µm, szemben az első és második generációs Foveros 50 és 36 µm-ével. Hasonló (10 µm) értékre majd a Foveros Direct lesz képes, de ez leghamarabb a 2023-as esztendő után érkezhet. Effektíve elmondható, hogy az AMD 3D-s tokozási technológiája inkább a Foveros Direct ellenfele, semmint az első és második generációs Foverosé.

Az AMD szerint a 3D-s tokozás meghatározó lesz a jövőben, és az egyre sűrűbb TSV léptetés megnyitja az utat igen érdekes integrációs lehetőségek felé is.