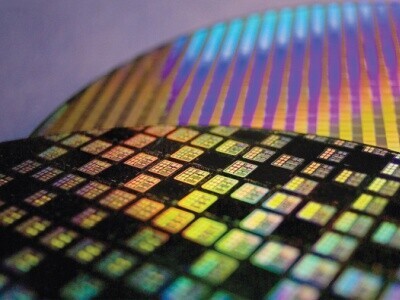

A TSMC még a nyáron vázolta fel érkező gyártástechnológiáit, de akkor még nem kaptak olyan nagy figyelmet a 3 és 2 nm-es node-ok, noha ezek említés szintjén azért szerepeltek a tervekben. Most a bérgyártó pont ezekről az eljárásokról beszélt, így kiderült, hogy nagyjából mire lehet majd számítani a jövőben.

A 3 nm-es csíkszélességen a vállalat még marad a FinFET tranzisztorstruktúránál, így viszonylag hamar be tudják vezetni az első, N3 jelzésű 3 nm-es node kísérleti gyártását, ami még idén megtörténik, míg a tömeggyártás a következő év második felében kezdődik meg, leginkább az esztendő vége felé. Ez az eljárás az 5 nm-es node-hoz viszonyítva 1,7-szer jobb tranzisztorsűrűséget fog kínálni, akár 30%-kal jobb fogyasztási adatok és 15%-kal jobb teljesítmény mellett. Lesz egy második generációs 3 nm-es node is N3E jelzéssel, ami egy év múlva követi az elsőt, és egyfajta optimalizálásnak tekinthető.

A 2 nm-es csíkszélesség már a nagy váltást hozza, ugyanis a TSMC is átáll az újabb, GAAFET tranzisztorstruktúrára, ami lényeges előnyöket biztosít majd. A cég itt a 2025-ös esztendőt említette céldátumként, ami valószínűleg a tömeggyártás megkezdését jelenti, de arról nincs adat, hogy ez a szóban forgó év melyik szakaszára vonatkozik.