Még idén tavasszal számoltunk be arról, hogy az AMD kipróbálhatja a HBM-et az új generációs EPYC processzorokon, és a Milan kódnevű platformnál létezik is egy olyan kísérleti rendszer, amely HBM-et támogató I/O lapkát használ. Arról még mindig nincs döntés, hogy ebből lesz-e kereskedelmi termék, de a próbák már aktívan zajlanak, és vélhetően a jövőre érkező, Genoa platformra vonatkozó elérhetőség van szem előtt tartva.

A szervergyártóktól most megtudtuk, hogy nem csak az AMD indul el ebbe az irányba, ugyanis az Intel HBM memóriavezérlőt helyezett a Sapphire Rapids kódnevű fejlesztésbe is. Erre ugyan még nem épül kísérleti rendszer, de a technológia biztosan benne van a lapkában, és vélhetőleg ki fogják majd próbálni a jövőben egy-egy mérnöki mintán. A Santa Clara-i óriáscég esetében szintén nem tudni, hogy kereskedelmi szinten bevetik-e, vagy esetleg egy későbbi Xeon generációt szem előtt tartva tesztelik a lehetőséget.

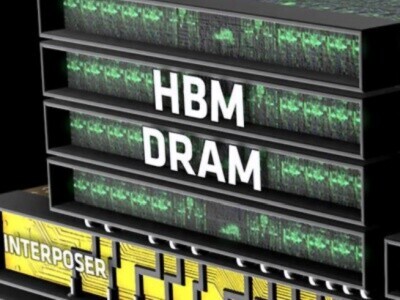

Az biztos, hogy a HBM idővel belopakodik az x86/AMD64-es szerverprocesszorokba. Persze a DDR5 lényeges előrelépést jelent majd, de ennél azért több kell, ha a magszám olyan intenzíven nő, ahogy az elmúlt időszakban, és jelen pillanatban több értelme van a HBM felé fordulni, mint a memóriacsatornák számát növelni. Ez köszönhető annak, hogy az újabb, HBM2E variánsok például igen komoly memória-sávszélességet biztosítanak egyetlen 1024 bites stackkel is. A jövő várhatóan az olyan hibrid konfigurációké, ahol a szerverprocesszoron lesz valamennyi HBM memória, míg az extrém, több TB-nyi kapacitást lehet biztosítani a DDR5-ös modulokon keresztül.